| Sign In | Join Free | My xxjcy.com |

|

- Home

- Products

- About Us

- Quality Control

- Contact Us

- Get Quotations

| Sign In | Join Free | My xxjcy.com |

|

Brand Name : Intel / Altera

Model Number : EP2AGZ300FF35C4N

Certification : Lead free / RoHS Compliant

MOQ : 1 pcs

Price : USD 3000-5000 pcs

Payment Terms : T/T, Western Union, Paypal, Trade Assurance, Credit Card

Supply Ability : 226 pcs

Delivery Time : 3-5 Day

Packaging Details : International Standard Packaging

Category : IC FPGA

Condition : Original 100%,Brand New and Original,New

Series : Arria II GZ

Number of Logic Array Blocks - LABs : 11920

Number of I/Os : 554 I/O

Operating Supply Voltage : 1.5 V to 3.3 V

Package / Case : FBGA-1152

Data Rate : 600 Mb/s to 6.375 Gb/s

Service : BOM Kitting

Lead time : In Stock,contact us

EP2AGZ300FF35C4N ALTERA FPGA Chip FBGA-1152 554 I/O Arria II GZ

| Product Attribute | Attribute Value |

|---|---|

| Intel | |

| FPGA - Field Programmable Gate Array | |

| Arria II GZ | |

| 298000 | |

| 11920 | |

| 554 I/O | |

| 1.5 V to 3.3 V | |

| 0 C | |

| + 70 C | |

| SMD/SMT | |

| FBGA-1152 | |

| Tray | |

| Data Rate: | 600 Mb/s to 6.375 Gb/s |

| Series: | Arria II GZ |

| Brand: | Intel / Altera |

| Embedded Block RAM - EBR: | 3725 kbit |

| Maximum Operating Frequency: | 540 MHz |

| Moisture Sensitive: | Yes |

| Number of Transceivers: | 16/24 Transceiver |

| Product Type: | FPGA - Field Programmable Gate Array |

| Factory Pack Quantity: | 24 |

| Subcategory: | Programmable Logic ICs |

| Total Memory: | 18413 kbit |

| Tradename: | Arria |

| Part # Aliases: | 969699 |

|

|

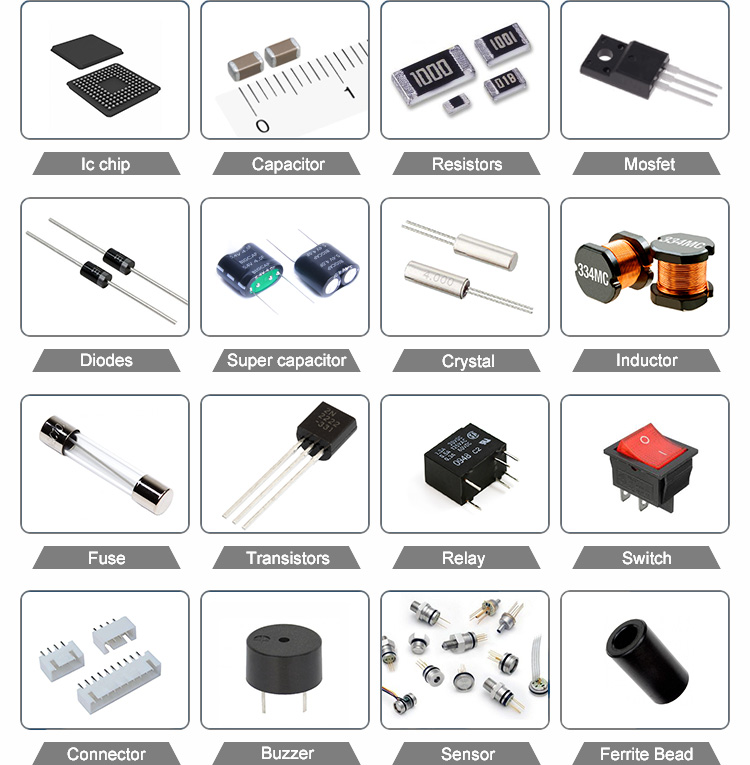

3.3V ALTERA FPGA Chip Images |